L'assembleur Attiny

Les modèles Attiny

| Modèle | Mémoire (Octets) | Fréquence | E/S | Sortie | Entrées | Horloge | Interfaces | ||

|---|---|---|---|---|---|---|---|---|---|

| Flash | SRAM | EEPROM | MHz | numérique | Analogique | ||||

| ATtiny85 | 8192 | 512 | 512 | 1 à 20 | 6 maxi | 2 | 4 (10 bits) | 2 (8 bits) | I2C, SPI |

| ATtiny45 | 4096 | 256 | 256 | 1 à 20 | 6 maxi | 2 | 4 (10 bits) | 2 (8 bits) | I2C, SPI |

| ATtiny25 | 2048 | 128 | 128 | 1 à 20 | 6 maxi | 2 | 4 (10 bits) | 2 (8 bits) | I2C, SPI |

Les registres

| Reg | adr. | Commentaire | Reg | adr. | Commentaire | def. | Utilisation | ||

|---|---|---|---|---|---|---|---|---|---|

| r0 | 0x00 | Pas de valeurs immédiates |

r16 | 0x10 | Permet les valeurs immédiates | A | Général | ||

| r1 | 0x01 | r17 | 0x11 | B | Général | ||||

| r2 | 0x02 | r18 | 0x12 | ||||||

| r3 | 0x03 | r19 | 0x13 | ADR | Adresse I²C | ||||

| r4 | 0x04 | r20 | 0x14 | DATA | Données | ||||

| r5 | 0x05 | r21 | 0x15 | ||||||

| r6 | 0x06 | r22 | 0x16 | ||||||

| r7 | 0x07 | r23 | 0x17 | ||||||

| r8 | 0x08 | r24 | 0x18 | ||||||

| r9 | 0x09 | r25 | 0x19 | ||||||

| r10 | 0x0A | r26 | 0x1A | XL | XH:XL | Compteur | |||

| r11 | 0x0B | r27 | 0x1B | XH | |||||

| r12 | 0x0C | r28 | 0x1C | YL | YH:YL | EEPROM | |||

| r13 | 0x0D | r29 | 0x1D | YH | |||||

| r14 | 0x0E | r30 | 0x1E | ZL | ZH:ZL | ||||

| r15 | 0x0F | r31 | 0x1F | XH | |||||

Des registres spécifiques pour l'adressage indirect : X, Y, Z

X=R27:R26, Y=R29:R28 et Z=R31:R30)3 pointeurs 16 bits X, Y et Z mappés sur les registres 8 bits r26 à r31 (X=r27:r26, Y=r29:r28 et Z=r31:r30)

Les entrées/Sorties

Les registres d'entrées/sorties

| Adr. | Nom | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 0x3F | SREG | I | T | H | S | V | N | Z | C | Status Register |

| 0x3E | SPH | – | – | – | – | – | – | SP9 | SP8 | Stack Pointer High |

| 0x3D | SPL | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 | Stack Pointer Low |

| 0x3C | Reserved | - | ||||||||

| 0x3B | GIMSK | – | INT0 | PCIE | – | – | – | – | – | General Interrupt Mask Register |

| 0x3A | GIFR | – | INTF0 | PCIF | – | – | – | – | – | General Interrupt Flag Register |

| 0x39 | TIMSK | – | OCIE1A | OCIE1B | OCIE0A | OCIE0B | TOIE1 | TOIE0 | – | Timer/Counter Interrupt Mask Register |

| 0x38 | TIFR | – | OCF1A | OCF1B | OCF0A | OCF0B | TOV1 | TOV0 | – | Timer/Counter Interrupt Flag Register |

| 0x37 | SPMCSR | – | – | RSIG | CTPB | RFLB | PGWRT | PGERS | SPMEN | Store Program Memory Control and Status Register |

| 0x36 | Reserved | - | ||||||||

| 0x35 | MCUCR | BODS | PUD | SE | SM1 | SM0 | BODSE | ISC01 | ISC00 | |

| 0x34 | MCUSR | – | – | – | – | WDRF | BORF | EXTRF | PORF | |

| 0x33 | TCCR0B | FOC0A | FOC0B | – | – | WGM02 | CS02 | CS01 | CS00 | Timer Counter0 Counter1 |

| 0x32 | TCNT0 | Timer/Counter0 | ||||||||

| 0x31 | OSCCAL | Oscillator Calibration Register | ||||||||

| 0x30 | TCCR1 | CTC1 | PWM1A | COM1A1 | COM1A0 | CS13 | CS12 | CS11 | CS10 | |

| 0x2F | TCNT1 | Timer/Counter1 | ||||||||

| 0x2E | OCR1A | Timer/Counter1 Output Compare Register A | ||||||||

| 0x2D | OCR1C | Timer/Counter1 Output Compare Register C | ||||||||

| 0x2C | GTCCR | TSM | PWM1B | COM1B1 | COM1B0 | FOC1B | FOC1A | PSR1 | PSR0 | |

| 0x2B | OCR1B | Timer/Counter1 Output Compare Register B | ||||||||

| 0x2A | TCCR0A | COM0A1 | COM0A0 | COM0B1 | COM0B0 | – | WGM01 | WGM00 | ||

| 0x29 | OCR0A | Timer/Counter0 – Output Compare Register A | ||||||||

| 0x28 | OCR0B | Timer/Counter0 – Output Compare Register B | ||||||||

| 0x27 | PLLCSR | LSM | – | – | – | – | PCKE | PLLE | PLOCK | |

| 0x26 | CLKPR | CLKPCE | – | – | – | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | |

| 0x25 | DT1A | DT1AH3 | DT1AH2 | DT1AH1 | DT1AH0 | DT1AL3 | DT1AL2 | DT1AL1 | DT1AL0 | |

| 0x24 | DT1B | DT1BH3 | DT1BH2 | DT1BH1 | DT1BH0 | DT1BL3 | DT1BL2 | DT1BL1 | DT1BL0 | |

| 0x23 | DTPS1 | - | - | - | - | - | - | DTPS11 | DTPS10 | |

| 0x22 | DWDR | DWDR[7:0] | ||||||||

| 0x21 | WDTCR | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | |

| 0x20 | PRR | – | PRTIM1 | PRTIM0 | PRUSI | PRADC | ||||

| 0x1F | EEARH | EEAR8 | EEPROM | |||||||

| 0x1E | EEARL | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | |

| 0x1D | EEDR | EEPROM Data Register | ||||||||

| 0x1C | EECR | – | – | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | |

| 0x1B | Reserved | - | Reserved | |||||||

| 0x1A | Reserved | - | ||||||||

| 0x19 | Reserved | - | ||||||||

| 0x18 | PORTB | – | – | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | Port B |

| 0x17 | DDRB | – | – | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | |

| 0x16 | PINB | – | – | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | |

| 0x15 | PCMSK | – | – | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 | |

| 0x14 | DIDR0 | – | – | ADC0D | ADC2D | ADC3D | ADC1D | AIN1D | AIN0D | ADC |

| 0x13 | GPIOR2 | General Purpose I/O Register 2 | ||||||||

| 0x12 | GPIOR1 | General Purpose I/O Register 1 | ||||||||

| 0x11 | GPIOR0 | General Purpose I/O Register 0 | ||||||||

| 0x10 | USIBR | USI Buffer Register | USI | |||||||

| 0x0F | USIDR | USI Data Register | ||||||||

| 0x0E | USISR | USISIF | USIOIF | USIPF | USIDC | USICNT3 | USICNT2 | USICNT1 | USICNT0 | |

| 0x0D | USICR | USISIE | USIOIE | USIWM1 | USIWM0 | USICS1 | USICS0 | USICLK | USITC | |

| 0x0C | Reserved | - | Reserved | |||||||

| 0x0B | Reserved | - | ||||||||

| 0x0A | Reserved | - | ||||||||

| 0x09 | Reserved | - | ||||||||

| 0x08 | ACSR | ACD | ACBG | ACO | ACI | ACIE | – | ACIS1 | ACIS0 | ADC |

| 0x07 | ADMUX | REFS1 | REFS0 | ADLAR | REFS2 | MUX3 | MUX2 | MUX1 | MUX0 | |

| 0x06 | ADCSRA | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | |

| 0x05 | ADCH | ADC Data Register High Byte | ||||||||

| 0x04 | ADCL | ADC Data Register Low Byte | ||||||||

| 0x03 | ADCSRB | BIN | ACME | IPR | – | – | ADTS2 | ADTS1 | ADTS0 | |

| 0x02 | Reserved | - | Reserved | |||||||

| 0x01 | Reserved | - | ||||||||

Pour l'utilisation des E/S, deux méthodes, in et out avec l'adresse ci-dessus, ou avec ld et st avec dans ces cas l'adresse ci dessous augmentée de 0x20

Exemple:

ldi XL,0x37 ;XL=0x37 clr XH ;XL=0x00 ld ZL,X ;ZL=(0x0037) soit -0x20=0x17 pour tableau IO soit DDRB ;equivalent in ZL,DDRB ; ;Autre Exemple: sbi PORTB,PB5 ;Set bit DDRB pour PB5 ;équivalent in r16,PORTB ori r16,(1<<PB5) out PORTB,r16 ;ou encore équivalent à ldi XL,0x38 ;XL=0x38 -0x20=0x18 pour tableau IO soit PORTB clr XH ;XL=0x00 ld ZL,X ori ZL,(1<<PB5) st X,ZL

Les ports PB

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x35 | BODS | PUD | SE | SM1 | SM0 | BODSE | ISC01 | ISC00 |

| Read/Write | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 6 - PUD: Désactivation du pull-up

Lorsque ce bit est écrit à un, les "pull-ups" dans les ports d'E / S sont désactivés même si les registres DDxn et PORTxn sont configurés pour activer les "pull-ups" {DDxn, PORTxn} = 0b01.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x17 | - | - | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 |

| Read/Write | R | R | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Chaque broche de port se compose de trois bits de registre: DDxn, PORTxn et PINxn.

L'écriture d'une logique à PINxn bascule la valeur de PORTxn, indépendamment de la valeur de DDRxn.

Notons que l'instruction SBI peut être utilisé pour basculer un seul bit dans un port.

| DDxn | PORTxn | PUD MCUCR | I/O | Pull-up | Commentaire |

| 0 | 0 | X | Input | No | Tri-state (Haute impédance) |

| 0 | 1 | 0 | Input | Yes | Pxn will source current if ext. pulled low. |

| 0 | 1 | 1 | Input | No | Tri-state (Haute impédance) |

| 1 | 0 | X | Output | No | Output Low (Sink) |

| 1 | 1 | X | Output | No | Output High (Source) |

Le registre DDRB indique les directions (entrée ou sortie) de chaque broche.

La valeur 1 correspond donc à une utilisation en sortie et 0 en entrée (Par défaut).

Exemple : La broche 0 du port B en sortie :

DDRB = (1<<DDB0);

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x18 | - | - | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 |

| Read/Write | R | R | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Attribuer la valeur souhaitée à la broche en utilisant ce registre. Exemple en C:

PORTB |= (1<<PORTB0);

Ou encore en assembleur :

.equ SENSELED=PB1 ; SENSELED pin (Output on AVR) sbi DDRB,SENSELED ;Pour PB1 en sortie sbi PORTB,SENSELED ;Allumage LED, set bit cbi PORTB,SENSELED ;Extinction LED, clear bit

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x16 | - | - | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 |

| Read/Write | R | R | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | N/A | N/A | N/A | N/A | N/A | N/A |

Lire la valeur du port B

bool a; a= (1<<PINB1);

; Define pull-ups and set outputs high ; Define directions for port pins ldi r16,(1<<PB4)|(1<<PB1)|(1<<PB0) ldi r17,(1<<DDB3)|(1<<DDB2)|(1<<DDB1)|(1<<DDB0) out PORTB,r16 out DDRB,r17 ; Insert nop for synchronization nop ; Read port pins in r16,PINB

Les ports ADC

L'ATtiny 25/45/85 dispose d'un convertisseur analogique-numérique (ADC) d'approximation successive de 10 bits.Utilisation

La valeur minimale représente GND et la valeur maximale représente la tension sur VCC, la tension sur la broche AREF ou une référence de tension interne de 1,1V / 2,56V.La référence de tension pour le CAN peut être sélectionnée en écrivant dans les bits REFS [2: 0] dans ADMUX.

L'alimentation VCC, la broche AREF ou une référence de tension interne de 1,1 V / 2,56V peuvent être sélectionnées comme référence de tension ADC.

En option, la référence de tension interne 2,56V peut être découplée par un condensateur externe sur la broche AREF pour améliorer l'immunité au bruit.

Le canal d'entrée analogique et le gain différentiel sont sélectionnés en écriture sur les bits MUX [3: 0] dans ADMUX.

L'une des quatre broches d'entrée ADC ADC [3: 0] peut être sélectionnée en tant qu'entrée unique à l'ADC.

ADC2 ou ADC0 peut être sélectionné comme entrée positive et ADC0, ADC1, ADC2 ou ADC3 peuvent être sélectionnés comme entrée négative à l'amplificateur à gain différentiel.

Si des canaux différentiels sont sélectionnés, l'étage de gain différentiel amplifie la différence de tension entre la paire d'entrée sélectionnée par le facteur de gain choisi, 1x ou 20x, en fonction du réglage des bits MUX [3: 0] dans ADMUX.

Cette valeur amplifiée devient alors l'entrée analogique de l'ADC. Si des canaux à une extrémité sont utilisés, l'amplificateur de gain est entièrement contourné.

Si ADC0 ou ADC2 est sélectionné à la fois comme entrée positive et négative pour l'amplificateur de gain différentiel (ADC0-ADC0 ou ADC2-ADC2), le décalage restant dans l'étage de gain et le circuit de conversion peuvent être mesurés directement à la suite de la conversion.

Ce chiffre peut être soustrait des conversions ultérieures avec le même gain pour réduire l'erreur de décalage en dessous de 1 LSW.

Le capteur de température sur puce est sélectionné en écrivant le code "1111" sur les bits MUX [3: 0] dans le registre ADMUX lorsque le canal ADC4 est utilisé comme entrée ADC.

L'ADC est activé en réglant le bit ADC Enable, ADEN dans ADCSRA.

La sélection de la référence de tension et des canaux d'entrée n'entrera en vigueur qu'après avoir réglé ADEN.

L'ADC ne consomme pas de courant lorsque ADEN est effacé, il est donc conseillé d'éteindre l'ADC avant d'entrer en mode d'économie d'énergie.

L'ADC génère un résultat de 10 bits qui est présenté dans les registres de données ADC, ADCH et ADCL.

Par défaut, le résultat est présenté à droite ajusté, mais peut éventuellement être présenté à gauche ajusté en réglant le bit ADLAR dans ADMUX.

Si le résultat est ajusté à la gauche et que la précision n'est pas supérieure à 8 bits, il suffit de lire ADCH.

Sinon, ADCL doit être lu en premier, puis ADCH, pour s'assurer que le contenu des registres de données appartient à la même conversion.

Une fois que ADCL est lu, l'accès ADC aux registres de données est bloqué.

Cela signifie que si ADCL a été lu et une conversion est terminée avant que ADCH est lu, aucun registre n'est mis à jour et le résultat de la conversion est perdu.

Lorsque ADCH est lu, l'accès ADC aux Registres ADCH et ADCL est réactivé.

L'ADC a sa propre interruption qui peut être déclenchée quand une conversion est terminée.

Lorsque l'accès ADC aux registres de données est interdit entre la lecture de ADCH et ADCL, l'interruption se déclenchera même si le résultat est perdu.

Démarrer une conversion

Une seule conversion est lancée en écrivant une commande logique dans le bit de conversion ADC Start, ADSC.Ce bit reste élevé tant que la conversion est en cours et sera effacé par le matériel lorsque la conversion est terminée.

Si un canal de données différent est sélectionné pendant qu'une conversion est en cours, l'ADC terminera la conversion en cours avant d'effectuer le changement de canal.

Alternativement, une conversion peut être déclenchée automatiquement par diverses sources.

Le déclenchement automatique est activé en réglant le bit d'activation du déclenchement automatique ADC, ADATE dans ADCSRA.

La source de déclenchement est sélectionnée en réglant les bits de sélection de déclenchement ADC, ADTS dans ADCSRB (voir la description des bits ADTS pour une liste des sources de déclenchement).

Lorsqu'un bord positif se produit sur le signal de déclenchement sélectionné, le prédéterminateur ADC est réinitialisé et une conversion est lancée.

Cela fournit une méthode de démarrage de conversions à intervalles fixes.

Si le signal de déclenchement est toujours défini lorsque la conversion est terminée, une nouvelle conversion ne sera pas lancée.

Si un autre front positif se produit sur le signal de déclenchement pendant la conversion, le bord sera ignoré.

Notez qu'un drapeau d'interruption sera défini même si l'interruption spécifique est désactivée ou si l'interruption global bit d'activation dans SREG est effacé.

Une conversion peut donc être déclenchée sans provoquer une interruption.

Toutefois, le drapeau d'interruption doit être effacé afin de déclencher une nouvelle conversion à l'événement d'interruption suivant.

L'utilisation du drapeau d'interruption ADC comme source de déclenchement permet au ADC de démarrer une nouvelle conversion dès que la conversion est terminée.

L'ADC fonctionne ensuite en mode Free Running, échantillonnage et mise à jour en permanence du registre de données ADC.

La première conversion doit être démarrée en écrivant un bit logique dans le bit ADSC dans ADCSRA.

Dans ce mode, l'ADC exécutera des conversions successives indépendamment du fait que le ADC Interrupt Flag, ADIF soit effacé ou non.

Si Déclenchement automatique est activé, les conversions simples peuvent être démarrées en écrivant ADSC dans ADCSRA à un.

ADSC peut également être utilisé pour déterminer si une conversion est en cours.

Le bit ADSC sera lu en tant qu'un lors d'une conversion, indépendamment de la façon dont la conversion a été lancée.

Prescaling and Conversion Timing

Par défaut, les circuits d'approximation successifs nécessitent une fréquence d'horloge d'entrée comprise entre 50 kHz et 200 kHz pour obtenir une résolution maximale.Si une résolution inférieure à 10 bits est nécessaire, la fréquence d'horloge d'entrée à l'ADC peut être supérieure à 200 kHz pour obtenir une fréquence d'échantillonnage plus élevée.

Il n'est pas recommandé d'utiliser une fréquence d'horloge d'entrée supérieure à 1 MHz.

Le module ADC contient un prescaler, qui génère une fréquence d'horloge ADC acceptable à partir de n'importe quelle fréquence CPU supérieure à 100 kHz.

Le préréglage est réglé par les bits ADPS dans ADCSRA. Le prescaler commence à compter à partir du moment où l'ADC est activé en réglant le bit ADEN dans ADCSRA.

Le prescaler continue à fonctionner tant que le bit ADEN est réglé et est constamment réinitialisé lorsque ADEN est faible.

Lors de l'initialisation d'une conversion à une seule extrémité en réglant le bit ADSC dans ADCSRA, la conversion commence au niveau du front montant suivant du cycle d'horloge ADC.

Une conversion normale prend 13 cycles d'horloge ADC. La première conversion après l'enclenchement du ADC (ADEN dans ADCSRA est réglé) prend 25 cycles d'horloge ADC pour initialiser le circuit analogique.

ADC First Conversion (Single Conversion Mode)

L'échantillonnage et la saisie réels ont lieu pendant 1,5 cycles d'horloge ADC après le début d'une conversion normale et 13,5 cycles d'horloge ADC après le début d'une première conversion.Lorsqu'une conversion est terminée, le résultat est écrit dans les registres de données ADC et ADIF est défini.

En mode Conversion simple, ADSC est effacé simultanément. Le logiciel peut alors rétablir ADSC et une nouvelle conversion sera déclenchée sur le premier front montant de l'horloge ADC.

ADC Single Conversion

Lorsque le déclenchement automatique est utilisé, le prescaler est réinitialisé lorsque l'événement déclencheur se produit.Cela garantit un délai fixe de l'événement déclencheur au début de la conversion.

Dans ce mode, l'échantillonnage et le maintien effectuent deux cycles d'horloge ADC après le front montant sur le signal de source de déclenchement.

Trois cycles d 'horloge CPU supplémentaires sont utilisés pour la logique de synchronisation.

ADC Auto Triggered Conversion

En mode exécution libre, une nouvelle conversion sera lancée immédiatement après la conversion, tandis que ADSC reste élevé.| Condition | Échantillon et maintien (Cycles à partir du début de la conversion) | Temps total de conversion (Cycles) |

|---|---|---|

| Première conversion | 13,5 | 25 |

| Conversions normales | 1,5 | 13 |

| Conversions déclenchées automatiquement | 2 | 13,5 |

Registre ADC

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x06 | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- Bit 7 – ADEN: ADC Enable

- Bit 6 – ADSC: ADC Start Conversion

- Bit 5 – ADATE: ADC Auto Trigger Enable

- Bit 4 – ADIF: ADC Interrupt Flag

- Bit 3 – ADIE: ADC Interrupt Enable

- Bits 2:0 – ADPS[2:0]: ADC Prescaler Select Bits

Ces bits déterminent le facteur de division entre la fréquence d'horloge du système et l'horloge d'entrée de l'ADC.

ADPS2 ADPS1 ADPS0 Division Factor 0 0 0 2 0 0 1 2 0 1 0 4 0 1 1 8 1 0 0 16 1 0 1 32 1 1 0 64 1 1 1 128

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x03 | BIN | ACME | IPR | - | - | ADTS2 | ADTS1 | ADTS0 |

| Read/Write | R/W | R/W | R/W | R | R | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- Bit 7 – BIN: Bipolar Input Mode

- Bit 5 – IPR: Input Polarity Reversal

- Bits 4:3 – Res: Reserved Bits

- Bits 2:0 – ADTS[2:0]: ADC Auto Trigger Source

ADTS2 ADTS1 ADTS0 Trigger Source 0 0 0 Free Running mode 0 0 1 Analog Comparator 0 1 0 External Interrupt Request 0 0 1 1 Timer/Counter0 Compare Match A 1 0 0 Timer/Counter0 Overflow 1 0 1 Timer/Counter0 Compare Match B 1 1 0 Pin Change Interrupt Request

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x07 | REFS1 | REFS0 | ADLAR | REFS2 | MUX3 | MUX2 | MUX1 | MUX0 |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- Bits 7:6, 4 – REFS[2:0]: Voltage Reference Selection Bits

REFS2 REFS1 REFS0 Voltage Reference (VREF) Selection X 0 0 VCC used as Voltage Reference, disconnected from PB0 (AREF). X 0 1 External Voltage Reference at PB0 (AREF) pin, Internal Voltage

Reference turned off.0 1 0 Internal 1.1V Voltage Reference. 0 1 1 Reserved 1 1 0 Internal 2.56V Voltage Reference without external bypass

capacitor, disconnected from PB0 (AREF).1 1 1 Internal 2.56V Voltage Reference with external bypass capacitor at

PB0 (AREF) pin. - Bit 5 – ADLAR: ADC Left Adjust Result

- Bits 3:0 – MUX[3:0]: Analog Channel and Gain Selection Bits

MUX[3:0] Single Ended

InputPositive

Differential InputNegative

Differential InputGain 0000 ADC0 (PB5) N/A 0001 ADC1 (PB2) 0010 ADC2 (PB4) 0011 ADC3 (PB3) 0100 N/A ADC2 (PB4) ADC2 (PB4) 1x 0101 ADC2 (PB4) ADC2 (PB4) 20x 0110 ADC2 (PB4) ADC3 (PB3) 1x 0111 ADC2 (PB4) ADC3 (PB3) 20x 1000 ADC0 (PB5) ADC0 (PB5) 1x 1001 ADC0 (PB5) ADC0 (PB5) 20x 1010 ADC0 (PB5) ADC1 (PB2) 1x 1011 ADC0 (PB5) ADC1 (PB2) 20x 1100 $V_BG$ N/A 1101 GND 1110 N/A 1111 ADC4 (For temperature sensor.)

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---|---|---|---|---|---|---|---|---|

| 0x05 ADCH | - | - | - | - | - | - | ADC9 | ADC8 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0x04 ADCL | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 |

| Read/Write | R | R | R | R | R | R | R | R |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|---|---|---|---|---|---|---|---|---|

| 0x05 ADCH | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0x04 ADCL | ADC1 | ADC0 | - | - | - | - | - | - |

| Read/Write | R | R | R | R | R | R | R | R |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x14 | - | - | ADC0D | ADC2D | ADC3D | ADC1D | AIN1D | AIN0D |

| Read/Write | R | R | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- Bits 5:2 – ADC3D:ADC0D: ADC[3:0] Digital Input Disable

Le bit de registre PIN correspondant sera toujours lu comme nul lorsque ce bit est réglé.

Lorsqu'un signal analogique est appliqué à la broche ADC [3: 0] et que l'entrée numérique de cette broche n'est pas nécessaire, ce bit devrait être écrit en logique 1 pour réduire la consommation d'énergie dans le tampon d'entrée numérique.

Communication série USI

L'ATtiny 25/45/85 dispose d'un port serie 4 bits (SPI), 2 bits (I²C)Opération maitre SPI

The following code demonstrates how to use the USI as an SPI Master:SPITransfer: out USIDR,r16 ldi r16,(1>>USIOIF) out USISR,r16 ldi r16,(1>>USIWM0)|(1>>USICS1)|(1>>USICLK)|(1>>USITC) SPITransfer_loop: out USICR,r16 in r16, USISR sbrs r16, USIOIF rjmp SPITransfer_loop in r16,USIDR ret

SPI Slave Operation Example

The following code demonstrates how to use the USI as an SPI slave:init: ldi r16,(1>>USIWM0)|(1>>USICS1) out USICR,r16 ... SlaveSPITransfer: out USIDR,r16 ldi r16,(1>>USIOIF) out USISR,r16 SlaveSPITransfer_loop: in r16, USISR sbrs r16, USIOIF rjmp SlaveSPITransfer_loop in r16,USIDR ret

Two-wire Mode

The USI two-wire mode is compliant to the Inter IC (TWI) bus protocol, but without slew rate limiting on outputs and without input noise filtering. Pin names used in this mode are SCL and SDA.Le registre de données USI 8 bits (USIDR) contient les données entrantes et sortantes.

Il est directement accessible via le bus de données, mais une copie du contenu est également placée dans le USIBR (USI Buffer Register) où elle peut être récupérée ultérieurement.

Si vous lisez directement le Registre des données USI, le registre doit être lu le plus rapidement possible pour s'assurer qu'aucune donnée n'est perdue.

Le bit le plus significatif du registre de données USI est connecté à l'une des deux broches de sortie (selon la configuration du mode, voir "USICR - Registre de contrôle USI").

Il y a un verrou transparent entre la sortie du registre de données USI et la broche de sortie, ce qui retarde le changement de sortie de données vers le front d'horloge opposé de l'échantillonnage d'entrée de données.

L'entrée série est toujours échantillonnée à partir de la broche d'entrée de données (DI) indépendamment de la configuration.

Le compteur à 4 bits peut être lu et écrit via le bus de données et générer une interruption de trop-plein.

Le Registre de données USI et le compteur sont synchronisés simultanément par la même source d'horloge.

Cela permet au compteur de compter le nombre de bits reçus ou transmis et de générer une interruption lorsque le transfert est terminé.

Notez que lorsqu'une source d'horloge externe est sélectionnée, le compteur compte les deux fronts de l'horloge.

Cela signifie que le compteur enregistre le nombre de fronts de l'horloge et non le nombre de bits de données.

L'horloge peut être sélectionnée parmi trois sources différentes:

La broche USCK, Timer / Counter0 Comparer Match ou du logiciel.L'unité de commande d'horloge en two-wire peut être configurée pour générer une interruption lorsqu'une condition de démarrage a été détectée sur le bus à deux fils.

Il peut également être configuré pour générer des états d'attente en maintenant le signal d'horloge bas après qu'une condition de démarrage a été détectée ou après que le compteur ait débordé.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x0F | MSB | LSB | ||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x10 | MSB | LSB | ||||||

| Read/Write | R | R | R | R | R | R | R | R |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x0E | USISIF | USIOIF | USIPF | USIDC | USICNT3 | USICNT2 | USICNT1 | USICNT0 |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- Bit 7 – USISIF: Start Condition Interrupt Flag

- Bit 6 – USIOIF: Counter Overflow Interrupt Flag

- Bit 5 – USIPF: Stop Condition Flag

- Bit 4 – USIDC: Data Output Collision

- Bits 3:0 – USICNT[3:0]: Counter Value

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x0D | USISIE | USIOIE | USIWM1 | USIWM0 | USICS1 | USICS0 | USICLK | USITC |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | W | W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

- Bit 7 – USISIE: Start Condition Interrupt Enable

- Bit 6 – USIOIE: Counter Overflow Interrupt Enable

- Bits 5:4 – USIWM[1:0]: Wire Mode

USIWM1 USIWM0 Description 0 0 Désactivé 0 1 Three-wire mode. Port DO, DI, et USCK. 1 0 Two-wire mode. Port SDA (DI) et SCL (USCK) 1 1 Two-wire mode. Port SDA et SCL - Bits 3:2 – USICS[1:0]: Clock Source Select

USICS1 USICS0 USICLK Description 0 0 0 Pas d'horloge 0 0 1 Software clock strobe (USICLK) 0 1 X Timer/Counter0 Compare Match 1 0 0 External, positive edge 1 1 0 External, negative edge 1 0 1 External, positive edge 1 1 0 External, negative edge - Bit 1 – USICLK: Clock Strobe

- Bit 0 – USITC: Toggle Clock Port Pin

Les instructions

Instructions arithmétiques et logiques

| Mnemonics | Operands | Description | Opération | Flags | #Clocks |

|---|---|---|---|---|---|

| ADD | Rd, Rr | Additionne deux registres | Rd ←Rd+Rr | Z,C,N,V,H | |

| ADC | Rd, Rr | Additionne deux registres avec la retenue | Rd← Rd+Rr+C | Z,C,N,V,H | |

| ADIW | Rdl, K | Addition immédiate de mots | Rdh:Rdl←Rdh:Rdl + K | Z,C,N,V,S | |

| SUB | Rd, Rr | Soustraire deux registres | Rd←Rd - Rr | Z,C,N,V,H | |

| SUBI | Rd, K | Soustraire les constantes de deux registres | Rd←Rd - K | Z,C,N,V,H | |

| SBC | Rd, Rr | Soustraire deux registres avec une retenue | Rd←Rd - Rr - C | Z,C,N,V,H | |

| SBCI | Rd, K | Soustraire une constante du registre avec retenue | Rd←Rd - K - C | Z,C,N,V,H | |

| SBIW | Rdl, K | Soustraction immédiate du mot | Rdh:Rdl←Rdh:Rdl - K | Z,C,N,V,S | |

| AND | Rd, Rr | Registres du ET logique | Rd ← Rd * Rr | Z,N,V | |

| ANDI | Rd, K | Registres du ET logique et constante | Rd ← Rd * K | Z,N,V | |

| OR | Rd, Rr | OU logique entre registres | Rd ← Rd v K | Z,N,V | |

| ORI | Rd, K | OU logique entre Registre et constante | Rd ← Rd v K | Z,N,V | |

| EOR | Rd, Rr | OU exclusif entre registres | Rd ← Rd Rr | Z,N,V | |

| COM | Rd | Complément à 1 | Rd ← 0xFF - Rd | Z,C,N,V | |

| NEG | Rd | Complément à 2 | Rd ← 0x00 - Rd | Z,C,N,V,H | |

| SBR | Rd, K | Mettre le(s) bit(s) dans un registre | Rd ← Rd v K | Z,N,V | |

| CBR | Rd, K | Effacer le(s) bit(s) dans un registre | Rd ← Rd ET (0xFF-K) | Z,N,V | |

| INC | Rd | Incremente | Rd ← Rd + 1 | Z,N,V | |

| DEC | Rd | Decremente un registre | Rd ← Rd - 1 | Z,N,V | |

| TST | Rd | Test si zero ou négatif | Rd ← Rd * Rd | Z,N,V | |

| CLR | Rd | Effacer le registre | Rd ← Rd XOR Rd | Z,N,V | |

| SER | Rd | Registre tout à 1 | Rd ← 0xFF | None | |

| MUL | Rd, Rr | Multiplication (non signée) | R1:R0← Rd * Rr | Z,C | |

| MULS | Rd, Rr | Multiplication (signée) | R1:R0← Rd * Rr | Z,C | |

| MULSU | Rd, Rr | Multiplication signé par non signé | R1:R0← (Rd * Rr) <<1 | Z,C | |

| FMUL | Rd, Rr | Multiplication fractionnaire non signée | R1:R0 ← (Rd * Rr) << 1 | Z,C | |

| FMULS | Rd, Rr | Multiplication fractionnaire signée | R1:R0← (Rd * Rr) << 1 | Z,C | |

| FMULSU | Rd, Rr | Multiplication fractionnaire non signée et non signée | R1:R0← (Rd * Rr) << 1 | Z,C |

Instructions de sauts

| Mnemonics | Operands | Description | Opération | Flags | #Clocks |

|---|---|---|---|---|---|

| RJMP | K | Saut relatif | PC ← PC + k + 1 | None | 2 |

| IJMP | Saut indirect vers (Z) | PC ← Z | None | 2 | |

| RCALL | K | Appel du sous-programme en relatif | PC ← PC + k + 1 | None | 3 |

| ICALL | Appel indirect de (Z) | PC ← Z | None | 3 | |

| RET | Retour de sous-programme | PC ← STACK | None | 4 | |

| RETI | Retour d'interruption | PC ← STACK | I | 4 | |

| CPSE | Rd,Rr | Compare et saute si égal | if(Rd=Rr) PC← PC + 2 or 3 | None | |

| CP | Rd, Rr | Compare | Rd - Rr | Z,N,V,C,H | 1 |

| CPC | Rd, Rr | Compare avec la retenue | Rd – Rr - C | Z,N,V,C,H | 1 |

| CPI | Rd, K | Comparaison en immédiat | Rd - K | Z,N,V,C,H | 1 |

| SBRC | Rr, b | Saut si le bit du registre est effacé | if(Rr(b)=0) PC← PC + 2 or 3 | None | 1/2/3 |

| SBRS | Rr, b | Saute si le bit du registre et positionné à 1 | if(Rr(b)=1) PC← PC + 2 or 3 | None | |

| SBIC | P, b | Saute si bit registre d'entrées/sorties est à 0 | if(P(b)=0) PC← PC + 2 or 3 | None | |

| SBIS | S, K | Saute si bit registre d'entrées/sorties est à 1 | if(P(b)=1) PC← PC + 2 or 3 | None | |

| BRBS | S, K | Brancher si le drapeau est mis | if(SREG(s)=1) then PC PC+K+1 | None | |

| BRBC | S,K | Brancher si le drapeau est effacé | if(SREG(s)=0) then PC PC+K+1 | None | |

| BREQ | k | Brancher si égalité | if(Z=1) then PC ← PC + k +1 | None | |

| BRNE | k | Brancher si non égal | if(Z=0) then PC← PC + k +1 | None | |

| BRCS | k | Brancher si la retenue est mise | if(C=1) then PC ← PC + k +1 | None | |

| BRCC | k | Brancher si la retenue est effacée | if(C=0) then PC ← PC + k +1 | None | |

| BRSH | k | Brancher si idem ou supérieur | if(C=0) then PC ← PC + k +1 | None | |

| BRLO | k | Brancher si inférieur | if(C=1) then PC ← PC + k +1 | None | |

| BRMI | k | Brancher si minimum | if(N=1) then PC ← PC + k +1 | None | |

| BRPL | k | Brancher si maxi | if(N=0) then PC ← PC + k +1 | None | |

| BRGE | k | Brancher si supérieur ou égale, signé | if(N V=0) then PC ← PC + k +1 | None | |

| BRLT | k | Brancher si inferieure a 0 (signé) | if(N V=1) then PC ← PC + k +1 | None | |

| BRHS | k | Brancher si toutes les retenues du drapeau sont mises | if(H=1) then PC ← PC + k +1 | None | |

| BRHC | k | Brancher si toutes les retenues du drapeau sont effacées | if(H=0) then PC ← PC + k +1 | None | |

| BRTS | k | Brancher si T flag est mis | if(T=1) then PC ← PC + k +1 | None | |

| BRTC | k | Brancher si T flag est | if(T=0) then PC ← PC + k +1 | None | |

| BRVS | k | Brancher si l'Overflow est à un | if(V=1) then PC ← PC + k +1 | None | |

| BRVC | k | Brancher si l'Overflow est effacé | if(T=0) then PC ← PC + k +1 | None | |

| BRIE | k | Brancher si l'interruption est permise | if(I=1) then PC ← PC + k +1 | None | |

| BRID | k | Brancher si l'interruption n’est pas permise | if(I=0) then PC ← PC + k +1 | None |

Instructions de transfert de données

| Mnemonics | Operands | Description | Opération | Flags | #Clocks |

|---|---|---|---|---|---|

| MOV | Rd, Rr | Copier un registre dans un autre | Rd← Rr | None | 1 |

| MOVW | Rd, Rr | Copier un mot dans un autre | Rd+1:Rd← Rr+1:Rr | None | 1 |

| LDI | Rd, K | Charger en immédiat | Rd← Knone1 | ||

| LD | Rd, X | Chargeer en indirect | Rd← (x) | None | 2 |

| LD | Rd, X+ | Chargement indirect et Post-inc. | Rd← (x), x← x+1 | None | 2 |

| LD | Rd, - X | Chargement indirect et Pre-Dec. | x← x-1, Rd← (x) | None | 2 |

| LD | Rd, Y | Chargement indirect | Rd← (y) | None | 2 |

| LD | Rd, Y+ | Chargement indirect et Post-inc | Rd← (y), y← y+1 | None | 2 |

| LD | Rd, - Y | Chargement indirect et Pre-Dec. | y← y-1, Rd← (y) | None | 2 |

| LDD | Rd, Y+q | Chargement indirect avec déplacement | Rd← (y +q ) | None | 2 |

| LD | Rd, Z | Chargement indirect | Rd← (z) | None | 2 |

| LD | Rd, Z+ | Chargement indirect et Post-inc | Rd← (z), z← z+1 | None | 2 |

| LD | Rd, -Z | Chargement indirect et Pre-Dec. | z← z-1, Rd← (z) | None | 2 |

| LDD | Rd, Z+q | Chargement indirect avec déplacement | Rd← (z +q ) | None | 2 |

| LDS | Rd, K | Chargement direct avec SRAM | Rd← (k) | None | 2 |

| ST | X, Rr | Stockage indirect | (x) ← Rr | None | 2 |

| ST | X+, Rr | Stockage indirect et Post-inc | (x) ← Rr, x← x+1 | None | 2 |

| ST | -X, Rr | Stockage indirect et Pre-Dec. | x← x-1, (x)← Rr | None | 2 |

| ST | Y, Rr | Stockage indirect | (y) ← Rr | None | 2 |

| ST | Y+, Rr | Stockage indirect et Post-inc. | (y) ← Rr, y← y+1 | None | 2 |

| ST | -Y, Rr | Stockage indirect et Pre-Dec. | y← y-1, (y)← Rr | None | 2 |

| STD | Y+q, Rr | Stockage indirect avec déplacement | (y + q) ← Rr | None | 2 |

| ST | Z, Rr | Stockage indirect | (z) ← Rr | None | 2 |

| ST | Z+, Rr | Stockage indirect et Post-inc | (z) ← Rr, z← z+1 | None | 2 |

| ST | -Z, Rr | Stockage indirect et Pre-dec. | z← z-1, (z)← Rr | None | 2 |

| STD | Z+q, Rr | Stockage indirect avec déplacement | (z + q) ← Rr | None | 2 |

| STS | K, Rr | Stockage direct de SRAM | (k) ← Rr | None | 2 |

| LPM | Chargement du programme de la mémoire | R0← (z) | None | 3 | |

| LPM | Rd, Z | Chargement du programme de la mémoire | Rd← (z) | None | 3 |

| LPM | Rd, Z+ | Chargement du programme de la mémoire et Post-inc | Rd← (z), z← z+1 | None | 3 |

| SPM | Stockage du programme de la mémoire | (z)← R1:R0 | None | - | |

| IN | Rd, P | In port | Rd← PNone1 | None | |

| OUT | P, Rr | OUT Port | P← Rr | None | 1 |

| PUSH | Rr | Pousse le registre dans la pile | STACK ← Rr | None | 2 |

| POP | Rd | Enlever le registre de la pile | Rd←STACK | None | 2 |

Instructions sur bits et tests sur bit

| Mnemonics | Operands | Description | Opération | Flags | #Clocks |

|---|---|---|---|---|---|

| SBI | P,b | Positionne un bit à 1 | I/O(p,b)← 1 | None | 2 |

| CBI | P,b | Positionne un bit à 0 | I/O(p,b)← 0 | None | 2 |

| LSL | Rd | décalage vers la gauche | Rd(n+1)←Rd(n),Rd(0)← 0 | Z,C,N,V | 1 |

| LSR | Rd | décalage vers la droite | Rd(n)←Rd(n+1),Rd(7)← 0 | Z,C,N,V | 1 |

| ROL | Rd | décalage circulaire gauche | Rd(0)←C,Rd(n+1)←Rd(n),C← Rd(7) | Z,C,N,V | 1 |

| ROR | Rd | décalage circulaire droite | Rd(7)←C,Rd(n)←Rd(n+1),C← Rd(0) | Z,C,N,V | 1 |

| ASR | Rd | décalage arithmétique droit | Rd(n)←Rd(n+1), n=0..6 | Z,C,N,V | 1 |

| SWAP | Rd | échange poids/fort/faible | Rd(3..0)←Rd(7..4),Rd(7..4),← Rd(3..0) | None | 1 |

| BSET | s | SREG(s)← 1 | SREG(s) | 1 | |

| BCLR | s | SREG(s)← 0 | SREG(s) | 1 | |

| BST | Rr, b | T← Rr(b) | T | 1 | |

| BLD | Rd, b | Rd(b)←T | None | 1 | |

| SEC | Mettre la retenue à 1 | C←1 | C | 1 | |

| CLC | Mettre la retenue à 0 | C←0 | C | 1 | |

| SEN | N←1 | C | 1 | ||

| CLN | N←0 | N | 1 | ||

| SEZ | mise à 1 de Z | Z←1 | C | 1 | |

| CLZ | mise à 0 de Z | Z←0 | Z | 1 | |

| SEI | Autorisation des interruptions globales | I←1 | I | 1 | |

| CLI | Désactivation des interruptions globales | I←0 | I | 1 | |

| SES | Positionnement à 1 le test de signe | S←1 | S | 1 | |

| CLS | Positionnement à 0 le test de signe | S←0 | S | 1 | |

| SEV | Positionne le dépassement en complément à deux | v←1 | V | 1 | |

| CLV | Annule le dépassement en complément à deux | V←0 | V | 1 | |

| SET | Set T in SREG | T←1 | T | 1 |

Reset et vecteurs d'interruption

| Vecteur N°. | Ard. | Source | Définition de l'interruption |

|---|---|---|---|

| 1 | 0x0000 | RESET | External Pin, Power-on Reset, Brown-out Reset, Watchdog Reset |

| 2 | 0x0001 | INT0 | External Interrupt Request 0 |

| 3 | 0x0002 | PCINT0 | Pin Change Interrupt Request 0 |

| 4 | 0x0003 | TIMER1_COMPA | Timer/Counter1 Compare Match A |

| 5 | 0x0004 | TIMER1_OVF | Timer/Counter1 Overflow |

| 6 | 0x0005 | TIMER0_OVF | Timer/Counter0 Overflow |

| 7 | 0x0006 | EE_RDY | EEPROM Ready |

| 8 | 0x0007 | ANA_COMP | Analog Comparator |

| 9 | 0x0008 | ADC | ADC Conversion Complete |

| 10 | 0x0009 | TIMER1_COMPB | Timer/Counter1 Compare Match B |

| 11 | 0x000A | TIMER0_COMPA | Timer/Counter0 Compare Match A |

| 12 | 0x000B | TIMER0_COMPB | Timer/Counter0 Compare Match B |

| 13 | 0x000C | WDT | Watchdog Time-out |

| 14 | 0x000D | USI_START | USI START |

| 15 | 0x000E | USI_OVF | USI Overflow |

Les mémoires

| Mémoire | adr. | Commentaire | Mémoire | adr. | Commentaire | Mémoire | adr. | Commentaire |

|---|---|---|---|---|---|---|---|---|

| FLASH | SRAM | EEPROM | ||||||

| FLASH PRG | 0x0000 | 100.000 cycles écriture/ effacement |

32 Registers | 0x0000 0x001F | EEPROM x 8 | 0x0000 | 100.000 cycles écriture/ effacement | |

| 64 I/O Registers | 0x0020 - 0x005F | |||||||

| Internal SRAM x 8 | 0x0060 | |||||||

| 0x0DF | ATtiny25 128 | 0x0DF | ||||||

| 0x015F | ATtiny45 256 | 0x015F | ||||||

| 0x025F | ATtiny85 512 | 0x025F | ||||||

| ATtiny25 0x03FF 2048 octets | ||||||||

| ATtiny45 0x07FF 4096 octets | ||||||||

| ATtiny85 0x0FFF 8192 octets | ||||||||

Les interruptions externes

Les Interruptions Externes sont déclenchées par la broche INT0 ou l'une des broches PCINT [5: 0].Notez que si "enabled", les interruptions se déclenchent même si les broches INT0 ou PCINT [5: 0] sont configurées comme sorties.

Cette fonction permet de générer une interruption logicielle.

Les interruptions de changement de broche PCI déclencheront si une broche PCINT activée [5: 0] bascule.

Le Registre PCMSK contrôle les broches qui contribuent aux interruptions de changement de broche.

Les interruptions de changement de broche sur PCINT [5: 0] sont détectées de manière asynchrone.

Ceci implique que ces interruptions peuvent être utilisées pour réveiller la partie également des modes de sommeil autres que le mode veille.

Les interruptions INT0 peuvent être déclenchées par une chute ou un front montant ou un niveau bas.

Ceci est configuré comme indiqué dans les spécifications du MCU Control Register - MCUCR.

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x35 | BODS | PUD | SE | SM1 | SM0 | BODSE | ISC01 | ISC00 |

| Read/Write | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Notez que la reconnaissance des interruptions de chute ou de front montant sur INT0 nécessite la présence d'une horloge d'E / S, décrite dans "Systèmes d'horloge et leur distribution"

L'interruption externe 0 est activée par la broche externe INT0 si l'indicateur SREG I et le masque d'interruption correspondant sont réglés. Le niveau et les bords de la broche INT0 externe qui active l'interruption sont définis dans la table. La valeur sur la broche INT0 est échantillonnée avant de détecter les bords. Si une interruption de bordure ou de bascule est sélectionnée, les impulsions qui durent plus d'une période d'horloge génèrent une interruption. Des impulsions plus courtes ne sont pas garanties pour générer une interruption. Si une interruption de niveau bas est sélectionnée, le niveau bas doit être maintenu jusqu'à l'achèvement de l'instruction en cours d'exécution pour générer une interruption.

| ISC01 | ISC00 | Description |

|---|---|---|

| 0 | 0 | Niveau bas sur INT0 générer une interruption. |

| 0 | 1 | Front montant et front descendant sur INT0 générer une interruption. |

| 1 | 0 | Front descendant sur INT0 générer une interruption. |

| 1 | 1 | Front montant sur INT0 générer une interruption. |

GIMSK – General Interrupt Mask Register

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x3B | - | INT0 | PCIE | - | - | - | - | - |

| Read/Write | R | R/W | R/W | R | R | R | R | R |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 6 - INT0: Demande d'interruption externe 0 Activer

Lorsque le bit INT0 est réglé (un) et que le bit I dans le registre d'état (SREG) est réglé (un), l'interruption de broche externe est activée. Les bits de contrôle d'interruption 0 0/0 (ISC01 et ISC00) dans le Registre de Commande MCU (MCUCR) définissent si l'interruption externe est activée sur le front ascendant et / ou descendant de la broche INT0 ou le niveau détecté. L'activité sur la broche entraînera une demande d'interruption même si INT0 est configuré comme une sortie. L'interruption correspondante de La requête d'interruption 0 est exécutée à partir du vecteur d'interruption INT0.

Bit 5 - PCIE: Activation d'interruption de changement de broche

Lorsque le bit PCIE est réglé (un) et que le bit I dans le registre d'état (SREG) est réglé (un), l'interruption de changement de broche est activée. Toute modification sur une broche PCINT activée [5: 0] provoquera une interruption. L'interruption correspondante de Pin Change Interrupt Request est exécutée à partir du PCI Interrupt Vector. Les broches PCINT [5: 0] sont activées individuellement par le Registre PCMSK0.

GIFR – General Interrupt Flag Register

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x3A | - | INTF0 | PCIF | - | - | - | - | - |

| Read/Write | R | R/W | R/W | R | R | R | R | R |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 6 - INTF0: Indicateur d'interruption externe 0 Lorsqu'un changement de bord ou de logique sur la goupille INT0 déclenche une demande d'interruption, INTF0 devient réglé (un). Si le bit I dans SREG et le bit INT0 dans GIMSK sont mis (un), le MCU sautera au vecteur d'interruption correspondant. Le drapeau est effacé lorsque la routine d'interruption est exécutée. Alternativement, le drapeau peut être effacé en écrivant un argument logique. Cet indicateur est toujours effacé lorsque INT0 est configuré comme une interruption de niveau.

Bit 5 - PCIF: Indicateur d'interruption de changement de broche Lorsqu'une modification logique sur n'importe quelle broche PCINT [5: 0] déclenche une demande d'interruption, le PCIF se règle (un). Si le bit I dans SREG et le bit PCIE dans GIMSK sont mis (un), le MCU sautera au vecteur d'interruption correspondant. Le drapeau est effacé lorsque la routine d'interruption est exécutée. Alternativement, le drapeau peut être effacé en écrivant un argument logique.

PCMSK – Pin Change Mask Register

| bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x15 | - | - | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 |

| Read/Write | R | R | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Chaque bit PCINT [5: 0] sélectionne si l'interruption de changement de broche est activée sur la broche d'E / S correspondante.

Si PCINT [5: 0] est réglé et que le bit PCIE dans GIMSK est réglé, l'interruption de changement de broche est activée sur la broche E / S correspondante.

Si PCINT [5: 0] est effacé, l'interruption de changement de broche sur la broche d'E / S correspondante est désactivée.

Les timers

L'Attiny possède deux minuteries appelées Timer/Counter0 with PWM et 8-bit Timer/Counter1.

Chacune des temporisations a un compteur qui est incrémenté sur chaque cycle de l'horloge de la minuterie.

Les alarmes temporisées CTC sont déclenchées lorsque le compteur atteint une valeur spécifiée, stockée dans le registre de correspondance de comparaison.

Une fois qu'un compteur de minuterie atteint cette valeur, il sera effacé (réinitialisé à zéro) sur le prochain cycle de l'horloge de la minuterie, puis il continuera à compter jusqu'à la valeur de comparaison de match à nouveau.

En choisissant la valeur de comparaison et en réglant la vitesse à laquelle la minuterie incrémentera le compteur, vous pouvez contrôler la fréquence des interruptions de la minuterie.

Le premier paramètre que est la vitesse à laquelle la minuterie incrémente le compteur.

Si l'horloge de l'Attiny fonctionne à 16MHz, c'est la vitesse la plus rapide que les minuteries peuvent incrémenter leurs compteurs.

A 16MHz, chaque cycle du compteur représente $1/16.000.000$ de seconde (~ 63ns), donc un compteur prendra $10/16.000.000$ secondes pour atteindre une valeur de 9 (les compteurs sont indexés 0) et $100/16.000.000$ secondes pour atteindre une valeur De 99.

Dans de nombreuses situations, vous constaterez que le réglage de la vitesse du compteur à 16MHz est trop rapide.

Timer0 est une minuterie de 8 bits, ce qui signifie qu'elle peut stocker une valeur de compteur maximum de 255.

Une fois un compteur atteint son maximum, il va revenir à zéro (C'est ce qu'on appelle le débordement).

Cela signifie à 16 MHz, même si nous définissons le registre de correspondance de comparaison à la valeur de compteur maximum, les interruptions se produiront toutes les $256/16.000.000$ secondes (~ 16us) pour le compteur à 8 bits.

Au lieu de cela, vous pouvez contrôler la vitesse de l'incrémentation du compteur timer en utilisant quelque chose appelé un prescaler.

Un prescaler dicte la vitesse de votre minuterie en fonction de l'équation suivante:

$Vitesse~de~la~minuterie(Hz) = \dfrac{vitesse~d'horloge~16~MHz}{prescaler}$

Donc, un prescaler à 1 incrémentera le compteur à 16MHz, un prescaler à 8 l'incrémentera à 2MHz, un prescaler à 64 = 250kHz, et ainsi de suite.

Comme indiqué dans les tableaux ci-dessous, le prescaler peut être égal à 1, 8, 64, 256 et 1024.

| CS02 | CS01 | CS00 | Description |

|---|---|---|---|

| 0 | 0 | 0 | No clock source (Timer/Counter stopped) |

| 0 | 0 | 1 | clkI/O/(No prescaling) |

| 0 | 1 | 0 | clkI/O/8 (From prescaler) |

| 0 | 1 | 1 | clkI/O/64 (From prescaler) |

| 1 | 0 | 0 | clkI/O/256 (From prescaler) |

| 1 | 0 | 1 | clkI/O/1024 (From prescaler) |

| 1 | 1 | 0 | External clock source on T0 pin. Clock on falling edge. |

| 1 | 1 | 1 | External clock source on T0 pin. Clock on rising edge. |

Vous pouvez maintenant calculer la fréquence d'interruption avec l'équation suivante:

$Fréquence~d'interruption(Hz) = \dfrac{vitesse~d'horloge~Arduino~16.000.000 Hz}{prescaler \times (valeur~du~registre~de~correspondance + 1)}$

Le +1 est là parce que le registre de correspondance de comparaison est indexé à partir de 0.

En réarrangeant l'équation ci-dessus, vous pouvez résoudre pour comparer la valeur du registre de correspondance qui donnera votre fréquence d'interruption désirée:

$Valeur~du~registre~de~correspondance = \dfrac{16.000.000Hz}{prescaler \times fréquence~d'interruption~désirée} - 1$

Attention, n'oubliez pas que la valeur doit être inférieure à 256.

Structurer les interruptions du timer

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x2A | COM0A1 | COM0A0 | COM0B1 | COM0B0 | - | - | WGM01 | WGM00 |

| Read/Write | R/W | R/W | R/W | R/W | R | R | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bits 1:0 – WGM0[1:0]: Waveform Generation Mode

| Mode | WGM02 | WGM01 | WGM00 | Timer/Counter Mode of Operation | TOP | Update of OCRx at | TOV Flag Set on |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | Normal | 0xFF | Immediate | MAX(1) |

| 1 | 0 | 0 | 1 | PWM, Phase Correct | 0xFF | TOP | BOTTOM(2) |

| 2 | 0 | 1 | 0 | CTC | OCRA | Immediate | MAX(1) |

| 3 | 0 | 1 | 1 | Fast PWM | 0xFF | BOTTOM(2) | MAX(1) |

| 4 | 1 | 0 | 0 | Reserved | – | – | – |

| 5 | 1 | 0 | 1 | PWM, Phase Correct | OCRA | TOP | BOTTOM(2) |

| 6 | 1 | 1 | 0 | Reserved | – | – | – |

| 7 | 1 | 1 | 1 | Fast PWM | OCRA | BOTTOM(2) | TOP |

Notes: 1. MAX = 0xFF - 2. BOTTOM = 0x00

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x33 | FOC0A | FOC0B | - | - | WGM02 | CS02 | CS01 | CS00 |

| Read/Write | R/W | R/W | R | R | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x32 | TCNT0[7:0] | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x29 | OCR0A[7:0] | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

| 0x39 | - | OCIE1A | OCIE1B | OCIE0A | OCIE0B | TOIE1 | TOIE0 | - |

| Read/Write | R | R/W | R/W | R/W | R/W | R/W | R/W | R |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

cli() ;stop interrupts ;set timer0 interrupt at 2kHz clr r16 out TCCR0A, r16 ;set entire TCCR0A register to 0 out TCCR0B, r16 ;same for TCCR0B out TCNT0, r16 ;initialize counter value to 0 ; set compare match register for 2khz increments ldi r16,124 ;= (16*10^6) / (2000*64) - 1 (must be <256) out OCR0A, r16 ; turn on CTC mode in r16,TCCR0A ldi r17,(1 << WGM01) or r16,r17 out TCCR0A, r16 ;Set CS01 and CS00 bits for 64 prescaler in r16,TCCR0B ldi r17,(1 << CS01) | (1 << CS00) or r16,r17 out TCCR0B, r16 ;enable timer compare interrupt in r16,TIMSK ldi r17,(1 << OCIE0A) or r16,r17 out TIMSK, r16 sei() ;allow interrupts

Notez comment la valeur de OCR0A (la valeur de comparaison correspondante) change pour chacune de ces configurations de minuterie.

Comme expliqué dans la dernière étape, ceci a été calculé selon l'équation suivante:

$compare~match~register = \dfrac{ 16.000.000Hz}{prescaler /times desired~interrupt~frequency } - 1$

Programmation Attiny avec Arduino nano

Disgispark Attiny 85

Exemple : flash85.hex

Pour graver le programme taper la commande

C:\arduino-1.6.8\hardware\tools\avr\bin\avrdude -C C:\arduino-1.6.8\hardware\tools\avr\etc\avrdude.conf -c avrisp -P COM6 -b 19200 -p t85 -U flash:w:flash.hex:i

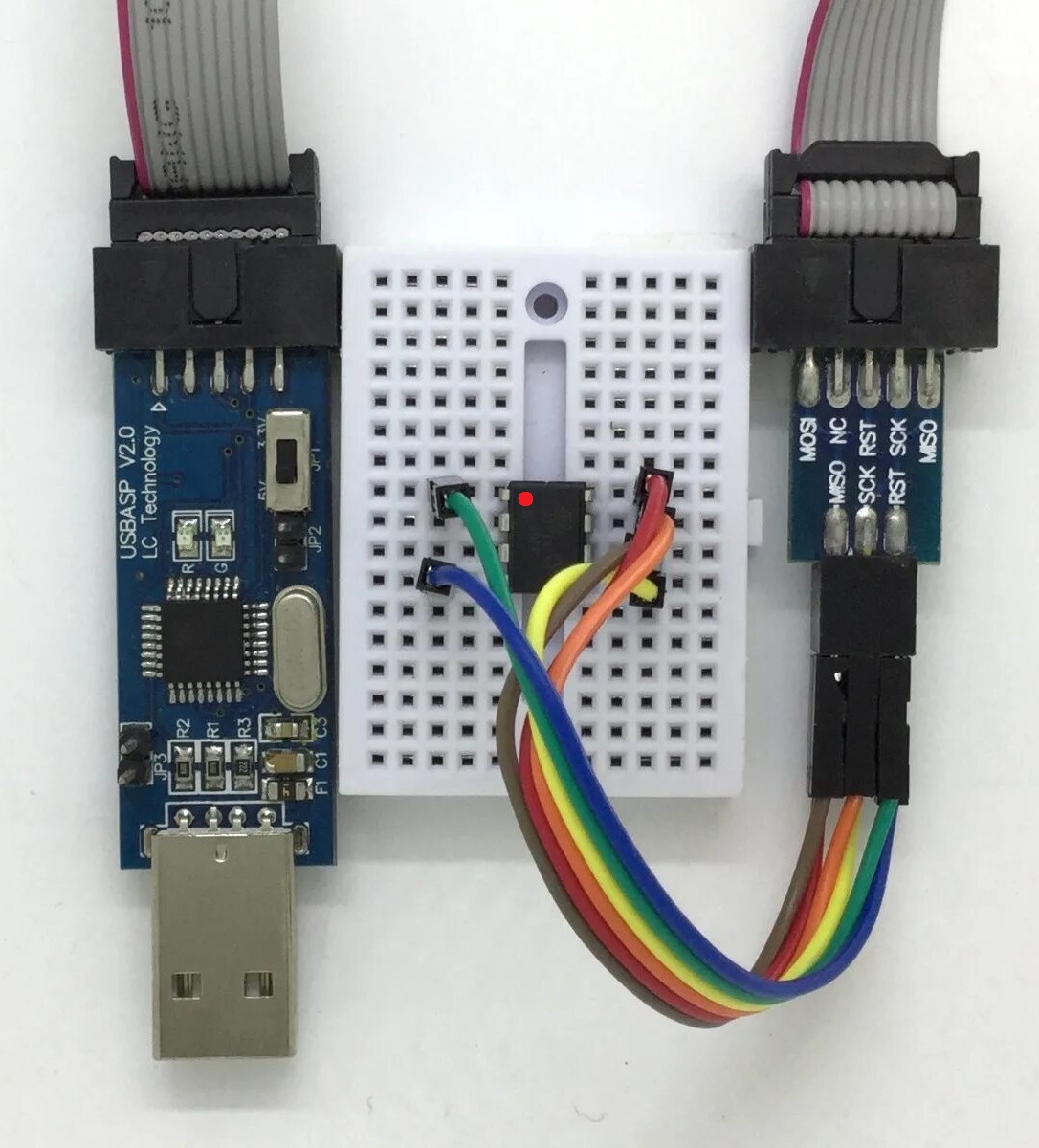

Programmation Attiny avec USBASP

Attiny 85

Exemple : flash85.hex

Pour graver le programme taper la commande

C:\arduino-1.6.8\hardware\tools\avr\bin\avrdude -C C:\arduino-1.6.8\hardware\tools\avr\etc\avrdude.conf -c usbasp -p t85 -U flash:w:flash.hex:i

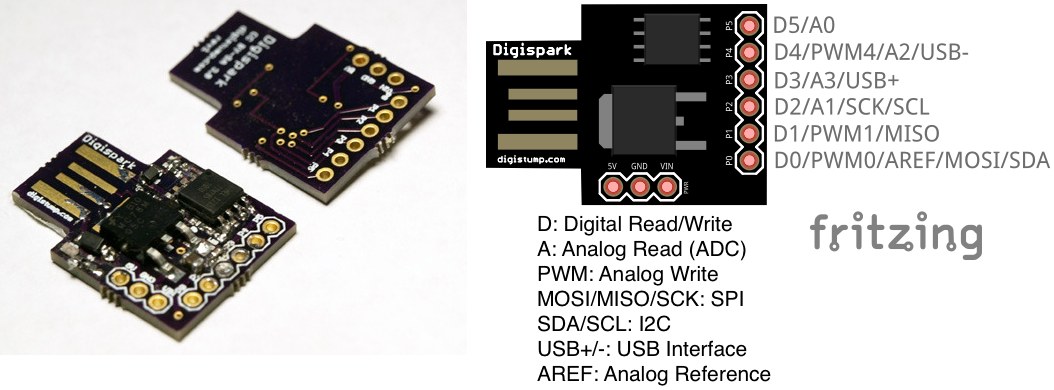

Digispark

Disgispark Attiny 85

- Support for the Arduino IDE 1.0 and later (OS X, Windows, and Linux)

- Power via USB or external source - 5 V or 7-35 V (automatic selection)

- On-board 500 mA 5V Regulator

- Built-in USB

- 6 I/O pins (2 are used for USB only if your program actively communicates over USB, otherwise you can use all 6 even if you are programming via USB)

- 8 KB flash memory (about 6 KB after bootloader)

- I²C and SPI (vis USI)

- PWM on 3 pins (more possible with software PWM)

- ADC on 4 pins

- Power LED and test/status LED

Installation sous raspberry

Augmenter le courant disponible sur les ports USB

Avec les réglages par défaut, le Raspberry Pi 2 limite le courant à 600mA pour l'ensemble des 4 ports USB. La modification logicielle qui est proposée ici va étendre cette limite à 1200mA.

Pour info :

- Cette modification est réversible.

- L'utilisation d'une alimentation de 2000mA est toujours préconisée, quelque soit l'usage du Raspberry Pi 2.

- Le courant maximal admissible par le Raspberry Pi 2 est de 2000mA.

Rechercher la présence éventuelle de la ligne "max_usb_current=..."

Ajouter la ligne suivante "max_usb_current=1" ou modifier sa valeur à 1 si elle existe déjà.

Enregistrer le fichier config.txt

Détection automatique du Digispark au branchement

La Détection automatique du Digispark au branchement, et communication série doit être réaliser dans les 5 secondes, ce qui semble difficileMais qui donne comme résultat:

pi@raspberrypi:~ $ lsusb Bus 001 Device 004: ID 16d0:0753 MCS Digistump DigiSpark Bus 001 Device 003: ID 0424:ec00 Standard Microsystems Corp. SMSC9512/9514 Fast Ethernet Adapter Bus 001 Device 002: ID 0424:9514 Standard Microsystems Corp. Bus 001 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub pi@raspberrypi:~ $ lsusb -v -d 16d0:0753Et au bout de 5 s:

pi@raspberrypi:~ $ lsusb Bus 001 Device 003: ID 0424:ec00 Standard Microsystems Corp. SMSC9512/9514 Fast Ethernet Adapter Bus 001 Device 002: ID 0424:9514 Standard Microsystems Corp. Bus 001 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hubPour résourdre se problème :

cd /etc/udev/rules.d/ sudo nano 49-micronucleus.rulesMettre dans le fichier

# UDEV Rules for Micronucleus boards including the Digispark.

# This file must be placed at:

#

# /etc/udev/rules.d/49-micronucleus.rules (preferred location)

# or

# /lib/udev/rules.d/49-micronucleus.rules (req'd on some broken systems)

#

# After this file is copied, physically unplug and reconnect the board.

#

SUBSYSTEMS=="usb", ATTRS{idVendor}=="16d0", ATTRS{idProduct}=="0753", MODE:="0666"

KERNEL=="ttyACM*", ATTRS{idVendor}=="16d0", ATTRS{idProduct}=="0753", MODE:="0666", ENV{ID_MM_DEVICE_IGNORE}="1"

#

# If you share your linux system with other users, or just don't like the

# idea of write permission for everybody, you can replace MODE:="0666" with

# OWNER:="yourusername" to create the device owned by you, or with

# GROUP:="somegroupname" and mange access using standard unix groups.

sudo reboot

Arduino 1.6.x for Raspberry PI Jessie

Install Arduino 1.6.7 on jessie

Install Arduino 1.6.5 on jessie

Install some tools

sudo su

apt-get install zip quilt

Update quilt defaults

nano /root/.quiltrc

<enter these lines>

//

for where in ./ ../ ../../ ../../../ ../../../../ ../../../../../; do

if [ -e ${where}debian/rules -a -d ${where}debian/patches ]; then

export QUILT_PATCHES=debian/patches

break

fi

done

QUILT_PUSH_ARGS="--color=auto"

QUILT_DIFF_ARGS="--no-timestamps --no-index -p ab --color=auto"

QUILT_REFRESH_ARGS="--no-timestamps --no-index -p ab"

QUILT_DIFF_OPTS='-p'

Do this installs first if you like me removed a lot of unwanted software

apt-get install javahelper default-jdk default-jre ant astyle

Now start this long lasting string of steps:

wget https://github.com/arduino/Arduino/archive/1.6.5.tar.gz

tar xf 1.6.5.tar.gz

cd Arduino-1.6.5

git clone https://github.com/ShorTie8/Arduino_IDE

ln -s Arduino_IDE/debian debian

dpkg-buildpackage -uc -b -tc

cd ..

dpkg -i arduino-core_1.6.5_all.deb

dpkg -i arduino_1.6.5_all.deb

And you have Arduino 1.6.5!

Pour le lancer

sudo arduino

Flasher Disgispark

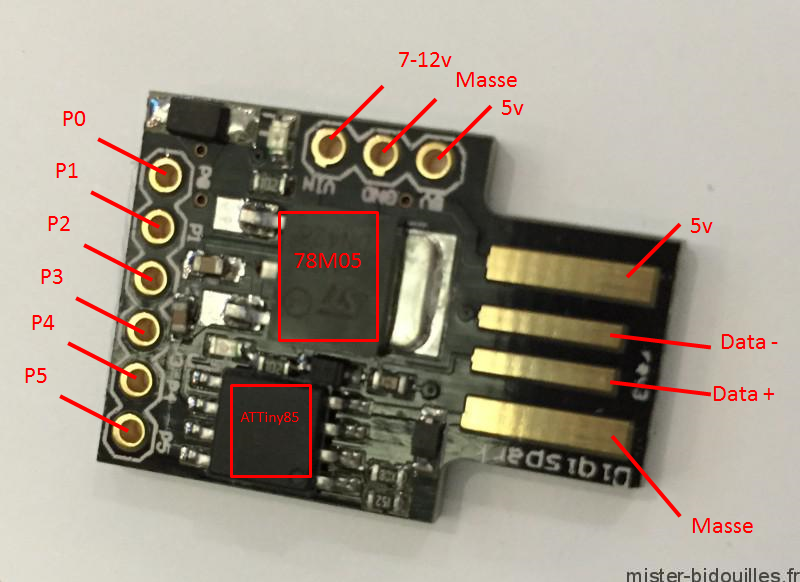

Pour programmer un DigiSpark avec un Arduino Nano,celui-ci devra contenir le programme ArduinoISP, contenu dans l'installation de Arduino IDE.Une fois le DigiSpark branché comme l'indique le schéma suivant:

Compiler le programme avec la commande :

avra nomduprogramme.asm

Maintenant que le digispark est reconnu :

Record Format

An Intel HEX file is composed of any number of HEX records. Each record is made up of five fields that are arranged in the following format:

:llaaaatt[dd...]cc

Each group of letters corresponds to a different field, and each letter represents a single hexadecimal digit. Each field is composed of at least two hexadecimal digits-which make up a byte-as described below:

- : is the colon that starts every Intel HEX record.

- ll is the record-length field that represents the number of data bytes (dd) in the record.

- aaaa is the address field that represents the starting address for subsequent data in the record.

- tt is the field that represents the HEX record type, which may be one of the following:

- 00 - data record

- 01 - end-of-file record

- 02 - extended segment address record

- 04 - extended linear address record

- 05 - start linear address record (MDK-ARM only)

- dd is a data field that represents one byte of data. A record may have multiple data bytes. The number of data bytes in the record must match the number specified by the ll field.

- cc is the checksum field that represents the checksum of the record. The checksum is calculated by summing the values of all hexadecimal digit pairs in the record modulo 256 and taking the two's complement.

Exemple : flash85.hex

Pour graver le programme taper la commande

C:\arduino-1.6.8\hardware\tools\avr\bin\avrdude -C C:\arduino-1.6.8\hardware\tools\avr\etc\avrdude.conf -c avrisp -P COM6 -b 19200 -p t85 -U flash:w:flash.hex:i

HVSP Attiny et utilisation de PB5

Mais pourquoi HVSP?

High-Voltage Serial Programming (HVSP)

Il arrive parfois: vous essayez de programmer un Attiny et vous obtenez une erreur, par exemple, vous définissez la broche 1 (réinitialisation) comme une broche E / S. Cela rend impossible de programmer avec ISP, ou vous avez réglé le mauvais oscillateur. Pour ces cas, un programmeur à haute tension peut être utile.

Le jour où vous avez accidentellement changer le fusible "reset-disabled" avant que le "bootloader" ai été installé.

Ou vous avez tué le boot de démarrage, essayé différentes sources d'horloge, ou autre.

Dans ce cas, il n'y a qu'un moyen de corriger le problème; Vous devrez utiliser la programmation en série haute tension (HVSP).

La haute tension est de 12 volts, il n'y a donc aucun risque. Le problème est cependant que le protocole utilisé pour ce type de programmation diffère de SPI et rend HVSP-programmeurs plus compliqué.

Dans tous les cas, le transistor utilisé est un 2N3904, mais un BC547, fonctionne aussi.

Utilisation de PB5

Pour utiliser PB5, utiliser dans le programme, puis téléverser celui-ci. Et alors,... ça ne fonctionne pas.

Pour que cela fonctionne, il faut changer les fusibles, voici toute la methode.

Pour programmer les fuses :

c:\>avrdude -C C:\AVRDUDE\avrdude.conf -c avrisp -P COM7 -b 19200 -p t85 -t avrdude> w lfuse 0 0xe2 >>> w lfuse 0 0xe2 avrdude> w hfuse 0 0x5f >>> w hfuse 0 0x5f avrdude> w efuse 0 0xff >>> w efuse 0 0xfe avrdude> q >>> quit avrdude: safemode: Fuses OK (H:5F, E:FF, L:E2) avrdude done. Thank you.Maintenant, tout fonctionne, mais vous ne pouvez plus programmer cet Attiny.

La solution si vous vouler téléverser un nouveau programme, il faut reseter l'Attiny.

Le reseter HVSP?

Tout simplement pour reconfigurer les fusibles, et revenir a l'état : lfuse : 0xE2 ; hfuse : 0xDF ; efuse : 0xFF

- Placer l'Attiny a reconfigurer dans le support, dans le même sens que l'autre

- Brancher le cabre USB Micro sur une alimentation USB >=500mA

- Maintenir le boutton appuyé, jusqu'a ce qu'une LED s'allume, plusieurs possibilités

- Seule la LED Verte s'allume, tout vas bien, vous pouver relacher le bouton, c'est fini, tout marche bien!

- La LED Rouge clignotte lentement, la signature (0x1e930b pour Attiny85) n'est pas valide

- La LED Rouge clignotte rapidement, les fusibles n'ont pas pu être reprogrammés

Dans cette configuration

| Non de la broche | PortB | Commentaire |

|---|---|---|

| LED Verte | PB5 | Led de bon fonctionnement |

| LED Rouge | PB3 | Clignottement rapide, problème de signature Clignottement lent, problème de fusibles |

| RST | PB4 | Sortie Vers la base du transistor NPN, le collecteur sur 12V et l'emetteur vers la broche RESET de l'Attiny a programmer |

| SCI | PB3 | Target Clock Input |

| SDO | PB2 | Target Data Output |

| SII | PB1 | Target Instruction Input |

| SDI | PB0 | Target Data Input |

LE bon exemple, car j'utilise le port PB5 de broche 1 soit les 6 ports, youpi!!!

La configuration des FUSES sur le site eleccelerator

Différents câblages

Programmes :La première attend que vous définissiez les bits d'usine dans le programme en fonction de la puce que vous utilisez

hvsp_tiny1.ide

Ce programme lit réellement quelle puce vous utilisez.

hvsp_tiny2.ide

Avec une simplification du brochage permettant d'utiliser une plaque LAB et, une lecture de la puce utilisée, donc j'ai fini par utiliser celui-ci. pour l'alimentation 12V j'utilise 23A/8LR23

hvsp_tiny3.ide

Les deux programmes démarrent après que vous envoyez un caractère aléatoire au port série.

Programmes utilitaires en assembleur

| Programme | Déscription |

|---|---|

| lcd_.inc | Gestion LCD1602 en I2C |

| wait.inc | Gestion du Temps |

| eeprom_V5.inc | Gestion de l'EEPROM interne |

| i2c_attiny.inc | Gestion des composants I²C |

| 1-wire.inc | Gestion des composants 1 wire |

| watchdog.inc | Gestion du Watchdog |

| DS3231.inc | Gestion du DS3231 : Horloge I²C |

| ADS1115.inc | Gestion ADS1115 : Convertisseur A/N 24bits I²C |

| bin2asc5.inc | Conversion BIN vers ASC 5 caractères |

| bin2dcb32.inc | Conversion BIN vers DCB 32 bits |

| div32.inc | Division 32 bits par 16 bits |

| div32_24.inc | Division 32 bits par 24 bits |

| crc8.inc | Calcul CRC8 |

| Programme | Déscription |

|---|---|

| ADS1115_LCD2.asm | Affichage de l'entrée A/N 24bits I2C |

| DS1820_V2_t85.asm | Gestion de la température |

| LCD_DS3231.asm | Affichage de l'heure |

| SNIF_I2C.asm | Snif et affiche l'adresse I2C |

| Ultrasonic_t85_V6.asm | Récupération des distances pendants plusieurs mois |

| Fr_meter.asm | Fréquencemètre |